ALUおよびアキュームレータ

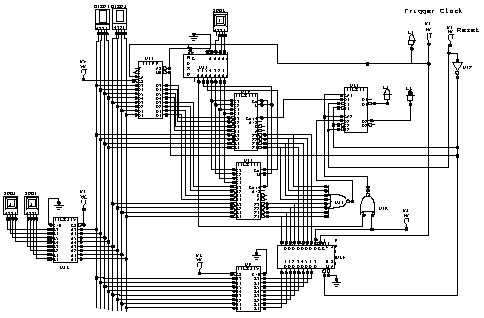

2.3.3 ALUおよびアキュームレータ動作確認用周辺回路を含むALU(算術論理演算装置)の回路構成を図2-9に示す.

図左側の縦に8本並列に並んでいるのがデータバスで,すぐ横に配置されているのがアキュームレータに用いた8ビットレジスタである.これは8ビットシフトレジスタの74199というTTLを用いた.

縦に2個配置されている74LS181は4ビットALUの論理ICで,A3-A0の4ビットとB3-B0の4ビットの演算結果がF3-F0に出力される.また,足し算の桁上がり結果等がCn+1に出力される.これを2個用いて8ビットの演算回路を構成した.

演算の種類は,S3からS1までと,Cn,Mの入力により制御される.命令レジスタの上位3ビットから演算の種類が決定されるので,16進キーの3ビットを用いて命令レジスタからの入力を想定し,それに応じた制御出力をPROMにより生成した.

PROMの内容は,CircuitMakerの画面上でPROMにカーソルを合わせて右クリックで内容表示を選択して確認できる.ADD,SUB,NANDおよび左SHIFT命令は実現できたが,74LS181の規格上,右シフトは本回路では実現できなかった.

ALUの演算結果は横向きに配置されている74199によりラッチ(保持)され,そのタイミングがトリガクロックにより与えられる.その出力は,74LS245のトライステートバッファを介してデータバスに接続されている.

データバスの左側には,バスに信号を与える16進キー2個がトライステートバッファを介して接続されている.データバスでは双方向にデータがやりとりされるので,レジスタまたはメモリの2ヶ所から同時にデータが出力されないように,出力信号はトライステートバッファを介して接続されなければならず,なおかつ,出力はどちらか一方のみが選択されなければならない.

演算結果において,桁上がりが生じた場合とゼロの値に成った場合は,Cn+1のキャリー信号と8入力NORにより検出され,それぞれキャリーフラグとゼロフラグとしてD-FF(74LS74)2個に記憶される.STORE命令時はACCのデータをALUを素通りさせてメモリへ書き込むが,この際フラグの状態が変化しないように,D-FFの入力を制御している.

図2-9 ALUの回路構成

ESP32 Wifi Bluetooth開発ボード |

Arduino Nano Every |

Raspberry Pi pico |

FPGA XILINX Artix-7 |