K-COMの回路構成

3.K-COMの回路構成

3.1 K-COMの回路構成

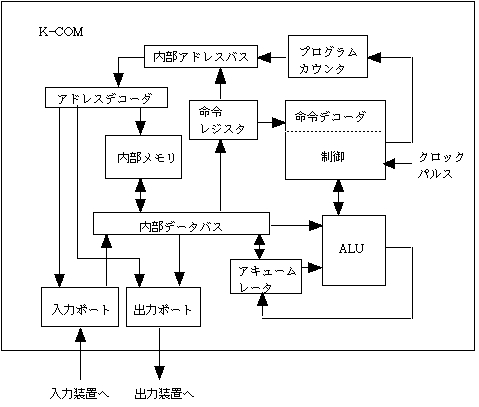

K-COMの回路構成について図3.1に示す.第1章で述べたコンピュータの回路構成とCPUの内部構造例(図1.4と図1.5)を基に考えると分かりやすい.通常は,CPU,メモリ,入出力ポート等,いくつかのLSIにより構成されているコンピュータを1つのLSIとして構成する事を想定した.そのため,メモリ,入出力ポートを内部に持ち,アドレス信号は内部アドレスバスを介して直接的に内部メモリ,入出力ポートに伝えられる.データバスについても同様に内部に備え,内部データバスを介して,メモリとアキュームレータ間のデータ転送,メモリとALUを直接接続して演算を行う.このように,図1.5と比較して図3.1はアドレスレジスタやデータレジスタを省いた構造になっている.

図3.1 K-COMの回路構成

3.2 レジスタ

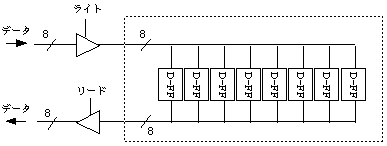

レジスタの具体的な回路構成について図3.2に示す.基本的には1ビットの情報を記憶できるフリップフロップ(図ではD-FF)を8個並列に並べて同時に読み書き出来る様な回路を構成したものである.レジスタの入力及び出力端子は他の回路と干渉しないように,トライステートバッファを介してデータバスに接続されている.

図3.2 レジスタの回路構成

3.3 ALUとアキュームレータ

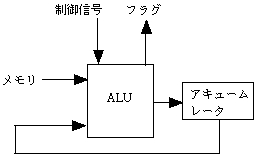

算術・論理演算装置(ALU)とアキュームレータの回路構成について図3.3に示す.アキュームレータとメモリから8ビットのデータをそれぞれALUに入力し,演算結果をアキュームレータに戻す.ALUは基本的には入力に8ビット×2+制御信号,出力に8ビット+フラグを持った組み合わせ論理回路である.実際には回路構成上,ALUの演算結果は,一旦ALUの出力に保持された後アキュームレータに転送される.どの様な演算を行うかは制御信号により決められる.演算結果が0になったか,桁あふれを生じたか等の情報はステータスフラグ(状態フラグ)に記憶される.

図3.3 ALUとアキュームレータの回路構成

3.4 メモリ

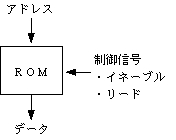

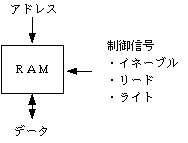

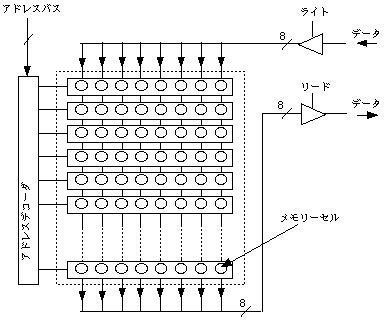

図3.4に示す様に,メモリには大別するとROM(Read OnlyMemory)とRAM(Random AccessMemory)の2種類がある.ROMは読み出し専用メモリで,アドレス信号を与えてデータを読み出す.制御信号はROMの動作を可能にするイネーブル信号とデータ読み出しのリード信号しかない.RAMはデータの読み出し及び書き込みができるメモリで,アドレス信号を与えてデータの読み出し及び書き込みを行う.制御信号はRAMの動作を可能にするイネーブル信号とデータ読み出しまたは書き込みをを指定する制御信号がある.実際のメモリの回路構成について図3.6にしめす.図中のメモリセルが1ビットの記憶回路を表す.メモリセル8個を使って1バイトのデータを表し,これがマトリクス状に配置されている.入力されたアドレスはデコードされ,対応する番地のメモリセルをそれぞれアクディブにし,データを並列にアクセスする.RAMの場合はメモリセルはフリップフロップなどの記憶素子からなり,読み出しと書き込みの信号線を持つ.ROMの場合のメモリセルは,0または1の固定出力を得るダイオードやトランジスタを用いた結線回路が用いられる.

図3.4 ROMとRAM

図3.5 メモリの回路構成

3.5 制御構造

制御構造とは,命令の各段階での手順を決定し,レジスタ,メモリ,ALU等の各回路の入出力ゲートを制御するタイミング信号を生成する順序回路を指す.従って,基本的には順序回路として考えればよい.CPUの制御構造には布線論理による順序回路とマイクロプログラム制御構造の2通りの実現手段があり,ここではマイクロプログラム制御方式を取り上げる.制御構造について図3.6に示す.制御論理回路,ステータスレジスタ,及びマイクロコードROMにより順序回路が構成されている.マイクロコードROMは各命令の制御手順は記憶されている読み出し専用メモリである.マイクロコードROMの出力が制御信号となり,各回路の入出力ゲートの制御信号となる.

制御論理回路には,命令レジスタ上位3ビットの命令コード,フラグ,及びマイクロコードROMが入力され,クロックに同期して次の状態がステータスレジスタに出力される.ステータスレジスタの値はデコードされ,マイクロコードROM内に記憶された制御信号が各回路の入出力ゲートに送られる.

図3.6 制御構造

3.6 I/Oポート

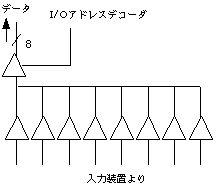

入力ポートの構成と出力ポートの構成を図3.7と図3.8にそれぞれ示す.入力ポートは,外部入力装置からの入力信号について,バッファを通して信号レベルをHigh,Lowのいずれかにして,トライステートバッファに加えられたI/Oデコーダの信号に同期してデータを取り込む構造になっている.

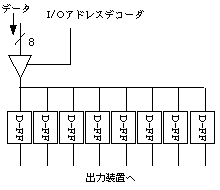

出力ポートは,トライステートバッファに加えられたI/Oデコーダの信号に同期してデータをD-FFに書き込む構造になっている.D-FFから常にHighかLowの信号が出力されているので外部装置は独自のタイミングで信号を受け取ることができる.

図3.7 入力ポートの構成 図3.8 出力ポートの構成

ESP32 Wifi Bluetooth開発ボード |

Arduino Nano Every |

Raspberry Pi pico |

FPGA XILINX Artix-7 |