HOME > pn接合シミュレーション

pn接合シミュレーション(定性的イメージ)

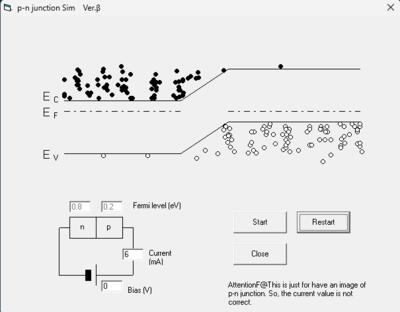

pn接合の定性的なシミュレーションです。これも約20年前に作ったものです。ゼロバイアスの時が以下の図で、左のn型半導体の部分は電子が多数、右のp型半導体の部分は正孔が多数になってます。この時、例えばn型の電子のエネルギー的に高いところの電子密度がp型の少数キャリアの電子密度と同じくなるようになっています。

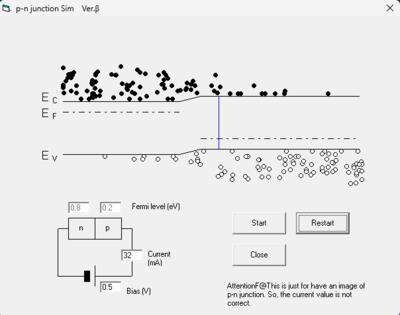

これに順方向バイアス、n型にマイナス、p型にプラスの電圧を加えると図のように、フェルミ順位に差ができてエネルギー障壁(電位障壁)が低くなり、多数キャリアがお互いに逆方向に拡散していき、電子ー正孔の再結合が起こり、順方向電流となります。

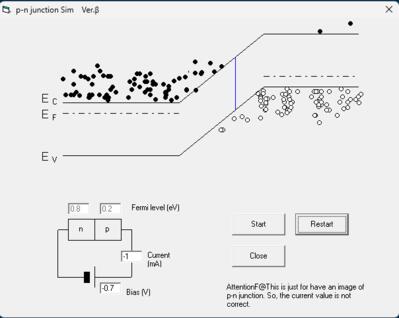

逆方向バイアスの時は、図のようにエネルギー障壁が高くなり、多数キャリアの移動はできなくなります。逆に空乏層近くの少数キャリが逆方向に流れ込んでわずかな逆方向電流となります。

これも、実際の電流スケールはけた違いの現象なので、あくまで定性的、視覚的に示すシミュレーションです。原理的な数式通りにでなく、逆に視覚的に見せるために細工したところが大変だった記憶があります。

ダウンロードはこちら、pn-junctionSim.zip

.exeに直リンクを貼ると警告がでるので、zip圧縮しました。警告出ると思いますが一応ウィルスチェックは通したので実行してみてください。

ESP32 Wifi Bluetooth開発ボード |

Arduino Nano Every |

Raspberry Pi pico |

FPGA XILINX Artix-7 |

コンテンツメニュー

- PICとは

- PIC関連リンク・参考書など

- PICの開発環境について

- MPLAB IDE

- HI-TECH PICC-LITE

- CCS社 PCW

- Wingcc

- 秋月PICプログラマー

- 赤外線送受信の実験

- 赤外線送受信(アナログ)

- ステップモータ制御

- PIC16F84Aでシリアル通信

- キッチンタイマー

- RC信号の監視

- プリンタ接続,PC-6021

- ポケコンでAVR

- I/Oとライントレースの実験

- Androidインストールメモ

- iPAQをiPhone風に

- App Inventor

- EKEN M001改造

- Android+Arduino

- 音声認識で動くロボット

- Bluetoothで送受信

- Bluetoothでロボット制御

- App Inventorサンプル

- App Inventorサンプル2

- RT-ADK/ADS

- Arduino+USBホストシールド

- ProcessingでAndroidアプリ

- ICカード分解(ETCカード)

- 赤外線リモコン受信モジュール

- PC9801(98note)分解

- 超音波加湿器の実験

- マイナスイオン発生器

- 回り続けるコマ

- 超音波小型カッター

- 電子レンジ用途外の使用

- 赤外線LEDの発光を確認

- 携帯テレビの延命措置

- 板金機とハンドプレス

- Edyカードの分解

- 100均のハトメで工作

- オープンキャンパス

- バスパワーメーター

- 3Dセンサモジュール

- マイクロシリアルサーボjコントローラ

- コアレスモータの結合

- レーザ式測域センサ

- GPS受信

- 掃除機分解

- アリの巣

- BSアンテナの分解

- サーボモータの実験

- 秋月のGPSモジュール

- 圧電振動ジャイロ

- 電子秤の分解

- 自分でエアコン洗浄

- 3角形のドライバー

- 動物撃退装置

- ホール素子,磁気センサ

- コテ先クリーナ

- 振動モータの分解

- PIXUS 50i 修理

- 磁気テープの磁性体を剥がす

- 1人前水出しアイスコーヒーの作り方

- CF-LV1のSSD換装

- AKI-H8 3048F メモ

- H8タイニー(3664)メモ

- 3664でLCD表示

- H8TinyでA/Dの実験

- H8TinyでPWMの実験

- μITRON

- H8で超音波センサの実験

- AKI-H8用書込みスイッチ

- 昔作ったマイクロマウス

- プロッタプリンタ

- ラジコングライダー

- KIROBO

- インドアプレーン

- 即席ラジコンボート

- IJEロボコン2008

- プリント基板露光器

- プリント基板作製

- SUMO MAN

- 大人の科学4ビットマイコン

- EAGLEでガーバー出力

- EAGLEの使い方メモ

- Gainer mini

- 金属探知機の自作

- 簡易カーブトレーサTr専用

- タイマーコンセント

- 8x5,8x8フォントエディタ

- VBでRFIDタイムスタンプ

- 卓上ファンの自作

- LED Cube (3x3x3)

- 自作3Dシステム

- 卓球マシンを循環式に

- CNCで基板加工

- 加速度をBluetooth送信

- くるくる飛行体

- スマートLCD

- ラジコン飛行機でFPV

- 反応速度を測るシステム

- 軽量なGPSロガー(16g)

- エフテック社のキット

- 製作前のあれこれ

- テスト用迷路の製作

- 回路試作

- ハーフサイズマウスの製作

- モータ駆動テスト

- センサを使った走行

- 左手法,拡張左手法

- 最短走行

- 競技に向けて

- おまけ,タイム自動計測

- マイクロマウスクラシック

- Pi:Co

- DCマウス

- 教材用マイクロマウス

- ITRONでマイクロマウス

- Arduinoでマイクロマウス

- mbedでマイクロマウス

- ブレッドボードでArduino

- Arduino書込機の自作

- Arduinoで温度計測

- Arduinoで倒立振子

- AVR超入門

- AVRをシリアルポートで書込み

- Arduinoで低周波発振器

- Arduinoで簡易オシロ

- AVRオシロスコープ

- 8x8LED電光掲示板

- AVR ISP抵抗値どこまで

- 物理実験用簡易計測器

- Metaboard

- V-USB

- アナログ文字入力表示装置

- さいもじ

- V-USBでHIDデバイス

- ArduinoでRFID

- ArduinoでFeliCa

- 超音波レンジファインダー

- Ethernetシールドメモ

- 移動ロボプラットフォーム

- 太陽光追尾装置

- SMSモニタリングシステム

- 微弱無線モジュール

- 1対多シリアル通信

- LEDデジタル時計

- SMS受信forPC

- 残像LEDディスプレイ

- RFIDで計測

- 微弱無線モジュール

- Arduinoの演習

- Da Vinci 32U

- DaVinciで外部割込み4本

- ボール&ビーム制御実験

- 気圧センサLPS331AP

その他の情報

関連リンク

(荒れたら消します)

(確認頻度低いです)