Quartus II入門

Quartus II入門 ~Verilogによる作成手順~

1.Quartus IIとは

Quartus IIとは,FPGAの主要メーカであるALTERA社の開発ツールである. Quartus II Web Editionが公開され,同社のホームページからダウンロードできる. 使用にはライセンス申請が必要で,詳細は以下のサイトにある.http://www.altera.co.jp/products/software/products/quartus2web/sof-quarwebmain.html

Quartus IIの使用法についても詳しい説明がWebにあるが,ここでは演習に必要最小限な説明を行う. Quartus IIは各種HDL(VHDL,Verilog,AHDL)に対応しているが,ここでは,Verilog-HDLによる簡単な 演習手順を示す.

2.Quartus IIの起動

図1はQuartus IIの起動画面である. HDLによる記述,論理合成,シミュレーション,実装などをサポートしているので,一連の作業はプロジェクト単位 で行う.

図1 QuartusIIの起動画面

3.プロジェクト作成

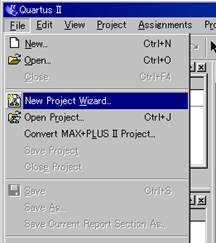

新規にプロジェクトを作成するには,FileメニューからNewProjectWizardを選択する(図2).

図2 ProjectWizard

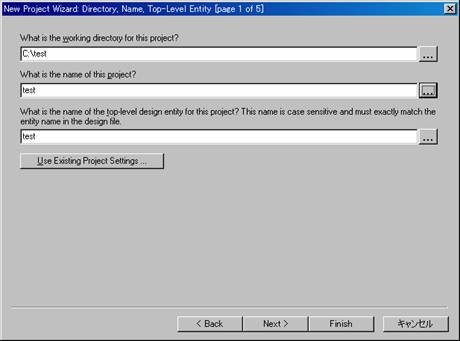

次に表示される画面はNextで進み,図3の画面に移る. 例として,Cドライブにtestというフォルダが作成されており,ここで作業を行う場合は, 1行目の入力でワーキングディレクトリとして指定する.

次にプロジェクト名を入力する.

いま,testフォルダ内にtestという名前でVerilogによる回路記述を作成してあるとすると, そのファイルを選択すればtestがプロジェクト名として入力され,その下のトップレベルデザインエンティティ名 (以下,トップエンティティと略記)もtestが自動で入力される. トップエンティティとは,回路が階層構造で記述されているとき,その最上位の回路のことである.

(階層構造でない単独の回路を用いるときはその回路をトップエンティティにする)

図3 作業ディレクトリ,プロジェクト名,トップエンティティの入力

ここで演習する記述内容について説明しておく.Verilogによる回路記述はテキストエディタで作成する. 拡張子は“.v”とする.test.vは,gand.vとgor.vの2つの回路を含んだ階層構造の上位階層の記述となっている. gand.vをリスト1,gor.v をリスト2,test.vをリスト3にそれぞれ示す.

リスト1のmoduleの後のgandが回路名である.最後はendmoduleでくくる. gandはaとbの2本の入力,cの出力を持つ回路でそれぞれinputとoutput文で宣言されている.

次のassign文によって入出力の関係が記述されている.

“&”記号はaとbの入力の論理積(AND)を意味する.

リスト2の回路gorは,gandと同様に2入力,1出力の回路で,aとbの論理和をcに出力する回路である.

リスト3のtestはa,b,c,dの4本の入力,x,y,zの3本の出力をもつ回路である.

先に定義されたgandとgorを呼び出してgandv,gorvの2つの回路を生成し,結線している. gandvはa,bの入力の論理積をxに出力し,gorvはc,dの入力の論理和をyに出力する. zはxとyの論理積としている.

ProjectWizardをNextで進めると,図4の画面となる.ここで,プロジェクトへのファイルの追加を行う. いま,testは階層構造を持ち,gandとgorの記述が必要なので,3つのファイルをプロジェクトに加える.

図4 プロジェクトへのファイルの追加

Nextで進むと,次は使用するデバイスの設定画面(図5)となる. ここで,回路を実装しようとするデバイスを選択する.(シミュレーションのみを行う場合は選択の必要なし) 後はNextで進み,最後にFinishを押すとプロジェクト作成が完了である.

図5 デバイスの設定

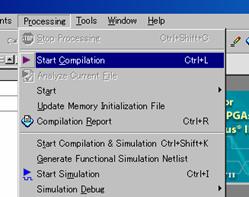

4.コンパイル

ProcessingメニューからStart Compilationを選択するとコンパイルが始まる(図5).

図6 コンパイル開始

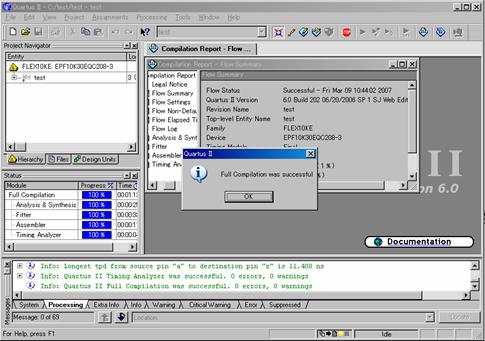

コンパイル中,いくつかのプロセスが行われ,エラーがなければ図7のようにコンパイル終了のメッセージが 表示される.左手のStatusに途中経過,画面下に各種情報(Info)やWarninigが表示される. エラーが検出された場合は,ここにエラー表示されるとともにコンパイルが中断する.

図7 コンパイル終了

5.シミュレーション

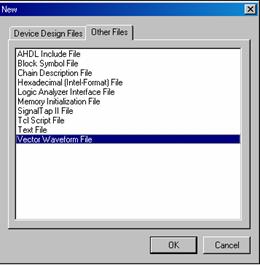

Verilogではテストベンチの記述を行うことができ,テストベンチによりシミュレーションを行うのが一般的である. 一方,Quartus IIではGUIを使って入力信号のテスト波形を作成し,シミュレーションを行うことができるので, ここではテスト波形によるシミュレーション手順を説明する.まず,テスト波形の作成を行う. FileメニューのNewを選択し,表示される画面のタブのOtherFilesをクリックし, Vector WaveForm Fileを選択する.

図8 Vector Wave Form Fileの新規作成

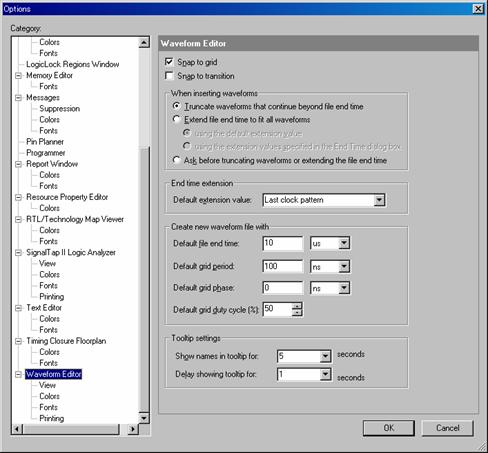

論理素子には信号の遅れ(ディレイ)があるので,高速な信号変化を与えるとディレイにより信号の対応が 見づらくなる.簡単な回路の動作確認をするときに十分に遅い信号変化を与えたほうが確認しやすいので, Grid size(Waveformの単位時間)を変更する.ToolsメニューのOptionsを選択し,図9の画面を表示させ, Wave Form Editorを選択した後,Default file end timeとDefault grid periodを設定する.

(ここでは,Default file end timeを10 us,Default grid periodを100 nsとしている)

図9 オプションの設定

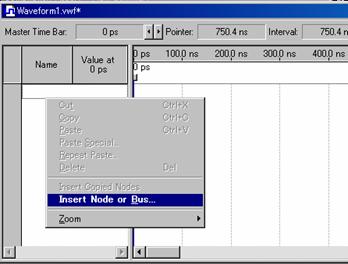

続いて,Wave Form Editorで波形を入力する.Name欄で右クリックし,Insert Node or Busを選択する.

図10 Wave Form Editor

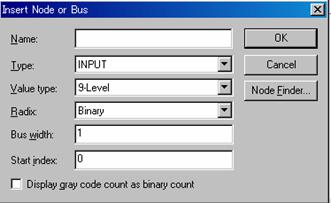

続いて現れる画面(図11)でNode Finderボタンを押す.

図11 Insert Node or Bus

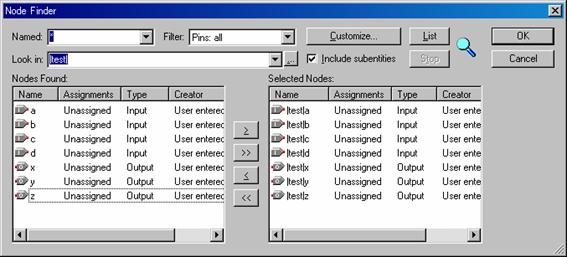

すると図12のNode Finder が表示される.ここで,Listボタンを押すと左側のNodes FoundにNode(入出力端子) の一覧が表示される.すべてのNodeを選んで中央の“>>”ボタンを押すと,右側のSelected Nodesに選択された Nodeの一覧が表示される.この後,OKを押し,Insert Node or Busでも続けてOKを押すと図13のように Waveformの画面にNodeが挿入される.

図12 Node Finder

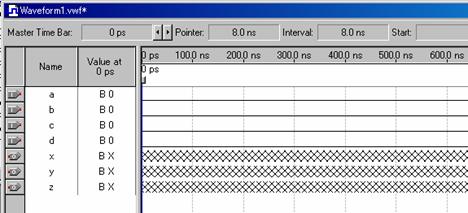

図13 Nodeが挿入されたWaveformの画面

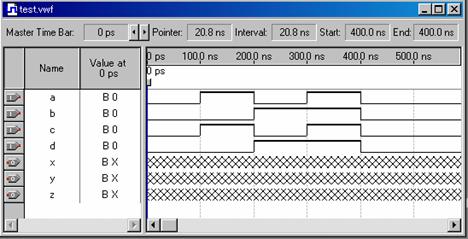

ツールバーからWaveform Edit Tool(

図14 波形の入力例

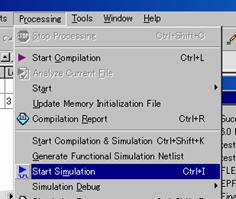

入力信号を合成された回路のシミュレーションは,ProcessingメニューからStart Simulationを選択する(図15).

図15 シミュレーション開始

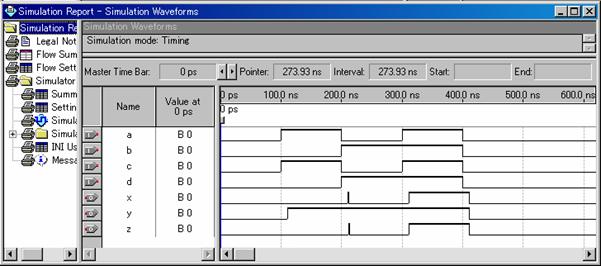

しばらく待つとシミュレーションが完了し,図16のようにシミュレーション結果が出力される. 図より,xはaとbの論理積,yはcとdの論理和,zはxとyの論理積であることが確認できる.

図16 シミュレーション結果

ESP32 Wifi Bluetooth開発ボード |

Arduino Nano Every |

Raspberry Pi pico |

FPGA XILINX Artix-7 |