クロックジェネレータ

K-COMは,レジスタ,メモリ,ALU等の回路間で,クロックに同期したデータ転送を行うことによって動作している.基本クロックだけでデータ転送を確実に行うことは不可能であるため,次のようなクロック発生回路を作成した.

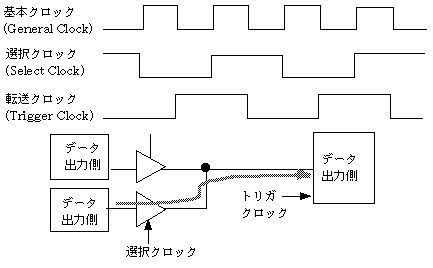

基本クロック(GeneralClock)を分周して2倍周期とし,両者を半周期ずらしたクロックである選択クロック(SelectClock)とトリガクロック(Trigger Clock)の2つを生成した.この様子を図2-7に示す.

選択クロックの立ち下がりを検出して,データの転送元と転送先を選択した後,トリガクロックの立ち上がりを検出して,データの転送を行う.選択クロックを立ち上がり検出としなかったのは,作成に用いた論理ICの信号の規格が立ち下がり検出となっていたためである.

図2-7 クロックとデータ転送の様子

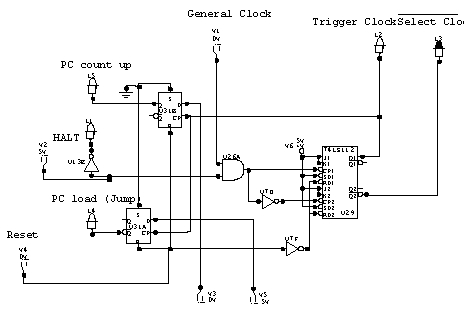

作成した回路図を図2-8に示す.

74LS112はJK-FFを2個収納した論理ICで,これをT-FFとして用いて,基本クロックおよび反転した基本クロックを与えて,選択クロックとトリガクロックを生成している.

図の左側のD-FFはプログラムカウンタのカウントアップとジャンプ時の飛び先読み込みのための信号を生成する回路である.プログラムカウンタに用いた論理ICの転送入力は,立ち上がりのみを検出するようにはなっていなかったため,選択クロックの立ち下がりで信号の不具合を生じた.そのため,プログラムカウンタの転送入力は,トリガクロックの立ち上がりで動作し,選択クロックの立ち下がりの影響を受けないD-FFで信号を用いた.

図2-8 クロック発生回路

ESP32 Wifi Bluetooth開発ボード |

Arduino Nano Every |

Raspberry Pi pico |

FPGA XILINX Artix-7 |