地元は半導体ブーム(バブル?)なので。

企業展示会とか行っていろいろ質問してると、何をされてるんですか?って聞かれて、以前半導体を...という話になってしまうので、どこかに書いておこうと思って、ホームページに半導体関連のカテゴリーを作りました。別のサイトを立ち上げたりするほどのコンテンツはないし。

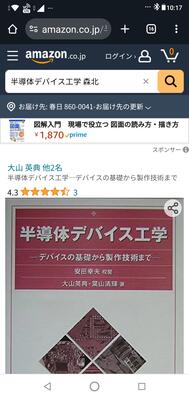

最初は、共著書についての紹介を書きました。

共著書:半導体デバイス工学について 2024.3.2

最初は、共著書についての紹介を書きました。

共著書:半導体デバイス工学について 2024.3.2

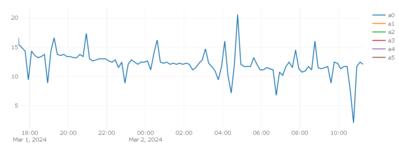

IoTで室温を時系列で記録して可視化、その2

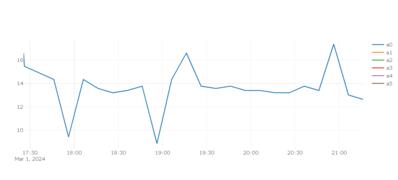

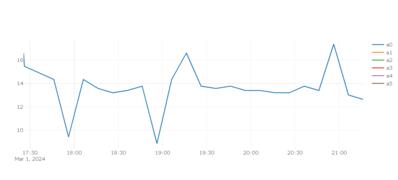

昨日の夕方からログを取り出して、今までのログ。

ノイズ多すぎですね。

ESP8266のアナログ入力のせいか、回路が悪いのか?

昨日書いたように考えられることはあるので、改良してまた動かしておきます。

IoT公開サーバーはこちら

ノイズ多すぎですね。

ESP8266のアナログ入力のせいか、回路が悪いのか?

昨日書いたように考えられることはあるので、改良してまた動かしておきます。

IoT公開サーバーはこちら

デジタル名刺を作ってみた、その2

今日は違うデジタル名刺サービスの宣伝が入ってきました。Meetというそうです。

申し込んでないけどやっぱりNFCでどっかのサイトに飛ばすのかなぁ。

SNSに飛ばせばワンクリックでフォローできたりするので自己紹介事業紹介等アピールしたい人には便利かなと思います。

昨日書いた、MFC Tools は結構いろいろできそうなので試してみました。

設定画面はこれ。いろんな項目があります。

ここで検索を選びサーチエンジンでamazonを選んで項目を入力すると、アマゾン商品がでるらしい。

でもやってみると、米国のamazonサイトに行って日本の商品は一部しかでませんでした。残念。

それならと、URLでamazonの短縮リンクを書きこんでみました。

結果はこの通り、著書がタッチで表示されました。

本の宣伝には便利。

広告

35枚入り NTAG213 NFC ステッカー, すべてのNFC電話機との互換

NTAG215 NFCタグ 10枚セット 円形シールタイプ ICONSHOP IC-nt215x10 ICカードリーダー用ブランクタグNFC Forum Type-2 504バイト

申し込んでないけどやっぱりNFCでどっかのサイトに飛ばすのかなぁ。

SNSに飛ばせばワンクリックでフォローできたりするので自己紹介事業紹介等アピールしたい人には便利かなと思います。

昨日書いた、MFC Tools は結構いろいろできそうなので試してみました。

設定画面はこれ。いろんな項目があります。

ここで検索を選びサーチエンジンでamazonを選んで項目を入力すると、アマゾン商品がでるらしい。

でもやってみると、米国のamazonサイトに行って日本の商品は一部しかでませんでした。残念。

それならと、URLでamazonの短縮リンクを書きこんでみました。

結果はこの通り、著書がタッチで表示されました。

本の宣伝には便利。

広告

35枚入り NTAG213 NFC ステッカー, すべてのNFC電話機との互換

NTAG215 NFCタグ 10枚セット 円形シールタイプ ICONSHOP IC-nt215x10 ICカードリーダー用ブランクタグNFC Forum Type-2 504バイト

デジタル名刺を作ってみた、その1

プレーリーカードというデジタル名刺があります。テレビで見て、Facebookにもしつこく広告が載って来るのでちょっと興味を持ちました。

どんな仕組み化と思ってサイトに行き、要はスマホをNFCカードにかざすとどっかのサイトに行くのかな、と思ったら似たようなことを自分でやってみてる人がいました。

Notion と MintRallyで、NFT付きのプレーリーカード(みたいなデジタル名刺)を作ってみた

https://note.com/yukkakiyo/n/n15dd9b2c9105

このサイトをみてNFCの書き込みツールがあるのを知ってやってみました。

Felicaカードは10年位前に買って持ってたので。

Androidスマホに NFC Tools - NFCへの書き込みツール をインストール。

スマホでNFCをONにしてツールを起動、カードをかざすと読む、書くのタブがあるので、書くの方でレコードを追加を押してホームページのURLを書き込みました。

アプリを閉じてから、カードをかざすとURLに飛びました。

最低限のプロフィールもホームページの方に書いてるので自分はこれで十分。

広告

NFCカード 白無地 10枚セット

PATIKIL NFCカード 30個 504バイト 85.5 x 54 mm 完全 プログラム可能 ブランク PVC カード タグ 電話 NFC対応デバイス用 ホワイト

どんな仕組み化と思ってサイトに行き、要はスマホをNFCカードにかざすとどっかのサイトに行くのかな、と思ったら似たようなことを自分でやってみてる人がいました。

Notion と MintRallyで、NFT付きのプレーリーカード(みたいなデジタル名刺)を作ってみた

https://note.com/yukkakiyo/n/n15dd9b2c9105

このサイトをみてNFCの書き込みツールがあるのを知ってやってみました。

Felicaカードは10年位前に買って持ってたので。

Androidスマホに NFC Tools - NFCへの書き込みツール をインストール。

スマホでNFCをONにしてツールを起動、カードをかざすと読む、書くのタブがあるので、書くの方でレコードを追加を押してホームページのURLを書き込みました。

アプリを閉じてから、カードをかざすとURLに飛びました。

最低限のプロフィールもホームページの方に書いてるので自分はこれで十分。

広告

NFCカード 白無地 10枚セット

PATIKIL NFCカード 30個 504バイト 85.5 x 54 mm 完全 プログラム可能 ブランク PVC カード タグ 電話 NFC対応デバイス用 ホワイト

IoTで室温を時系列で記録して可視化

せっかくIoTサーバーを作ったのでとりあえず何か動かしておこうと思って作り出しました。

まず、秋月電子通商さんのESP8266を搭載したESP-WROOM-02開発ボードを使います。

まず、ESP8266のライブラリを一通りインストール。

その後、サンプルプログラムを探すと、BasicHttpClientというものがあります。

ESP8266でWifiに接続してWebにアクセスするのです。

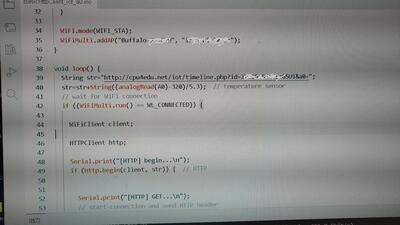

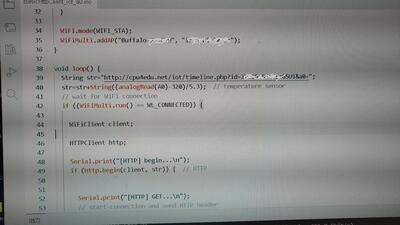

32行目の WiFiMulti.addAP("SSID", "PASSWORD");

に接続するWifiのIISDとパスワードを入力、

47行目の if (http.begin(client, "http://jigsaw.w3.org/HTTP/connection.html")) {

でhttp....の部分にアクセスしたいURLを入力します。

公開したIoTサーバーでメールアドレスを登録してIDを作成したら、URLの所にIDとデータを含めて送ります。

IDとa0=まで書き込んだURLを文字列に入れ、その後に AnalogRead で読み取った数値をセンサに固有の加工して文字列に追記して送ればよいです。

以下の写真の例のように、39,40行で文字列を作って49行目で送ります。

ここでは見えてませんが、下の方でループの待ち時間をdelay(600000)、つまり10分にしています。

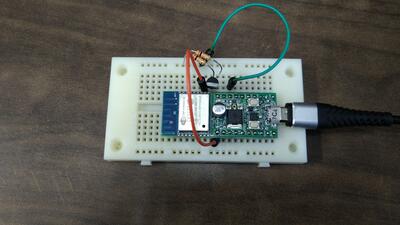

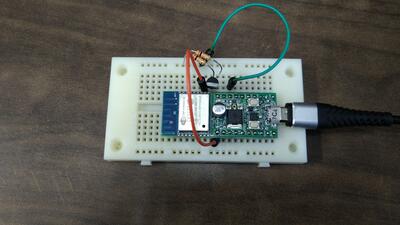

回路はこちら、LM61というアナログ温度センサの出力を読み取っているのですが、温度100度で1.6Vの出力となり、ESP8266のアナログ入力は約1Vで飽和してしまうのでそのままでは読み取れず、10kΩの抵抗2本で分圧して半分の電圧にしてESP-WROOM-02開発ボードの18番ピンに与えています。

10分間隔でログを残して、IDでアクセスして可視化した例はこちら。

例として簡単な回路とプログラムで作りましたが、改良すべき点があります。

回路の配線を少なくするためこじんまり配線してますが、マイコンボードは通電すると多少発熱するので、センサとマイコンはできるだけ離すべきです。

プログラムも1度だけセンサを読み取るのでは誤差の要因となります。

Wifiにアクセスするときは数100mAの電流を流すのでWiFiにアクセスするタイミングとセンサ読み取りのタイミングは離す方が良くて、センサの読み取りも1度でなくて数回読んで積算、平均化した方が良いです。

電源強化のためにキャパシタンスも追加した方がいいでしょう。

IoT公開サーバーはこちら

まず、秋月電子通商さんのESP8266を搭載したESP-WROOM-02開発ボードを使います。

まず、ESP8266のライブラリを一通りインストール。

その後、サンプルプログラムを探すと、BasicHttpClientというものがあります。

ESP8266でWifiに接続してWebにアクセスするのです。

32行目の WiFiMulti.addAP("SSID", "PASSWORD");

に接続するWifiのIISDとパスワードを入力、

47行目の if (http.begin(client, "http://jigsaw.w3.org/HTTP/connection.html")) {

でhttp....の部分にアクセスしたいURLを入力します。

公開したIoTサーバーでメールアドレスを登録してIDを作成したら、URLの所にIDとデータを含めて送ります。

IDとa0=まで書き込んだURLを文字列に入れ、その後に AnalogRead で読み取った数値をセンサに固有の加工して文字列に追記して送ればよいです。

以下の写真の例のように、39,40行で文字列を作って49行目で送ります。

ここでは見えてませんが、下の方でループの待ち時間をdelay(600000)、つまり10分にしています。

回路はこちら、LM61というアナログ温度センサの出力を読み取っているのですが、温度100度で1.6Vの出力となり、ESP8266のアナログ入力は約1Vで飽和してしまうのでそのままでは読み取れず、10kΩの抵抗2本で分圧して半分の電圧にしてESP-WROOM-02開発ボードの18番ピンに与えています。

10分間隔でログを残して、IDでアクセスして可視化した例はこちら。

例として簡単な回路とプログラムで作りましたが、改良すべき点があります。

回路の配線を少なくするためこじんまり配線してますが、マイコンボードは通電すると多少発熱するので、センサとマイコンはできるだけ離すべきです。

プログラムも1度だけセンサを読み取るのでは誤差の要因となります。

Wifiにアクセスするときは数100mAの電流を流すのでWiFiにアクセスするタイミングとセンサ読み取りのタイミングは離す方が良くて、センサの読み取りも1度でなくて数回読んで積算、平均化した方が良いです。

電源強化のためにキャパシタンスも追加した方がいいでしょう。

IoT公開サーバーはこちら